Le Gestionnaire de plug-inde™ MegaWizard ne dispose pas d’une option permettant de sélectionner ATX PLL tout en créant un MAC Ethernet avec PCS et PMA 1000BASE-X/SGMII. Stratix® les périphériques IV GX/GT disposent d’unell de transmission auxiliaire (ATX) supplémentaire pouvant être utilisée dans les émetteurs-récepteurs Ethernet MAC 1000BASE-x. Les étapes ci-dessous vous montrent comment utiliser ATX PLL dans la conception de l’émetteur-récepteur.

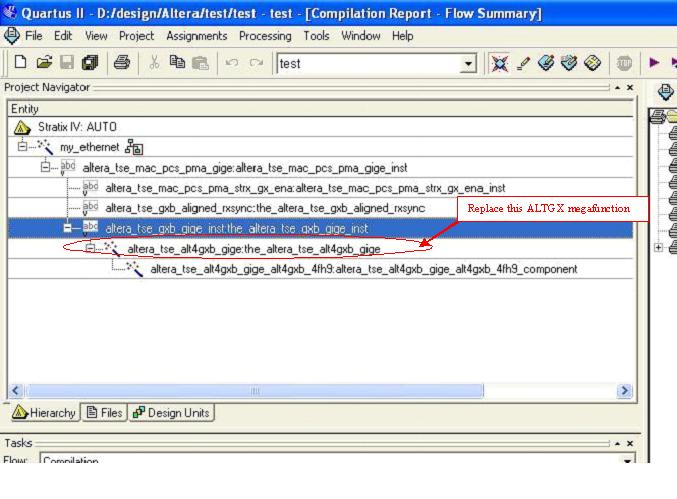

1. Pour utiliser la PLL ATX dans un MAC Ethernet avec PCS et PMA 1000BASE-X/SGMII, vous devez exécuter votre conception dans Quartus. Développez toute la hiérarchie de votre conception après l’analyse et la synthèse ; Vous verrez l’AltGX Megafunction dans votre IP MAC Ethernet.

2. Vous pouvez ouvrir le cœur ALTGX avec le Gestionnaire de plug-in Megawizard en double-cliquez dessus. Vous pouvez voir tous les paramètres effectués par Megawizard à ce stade. Malheureusement, l’option d’utilisation ATX PLL (sous les paramètres PLL) est grisée.

3. Accédez à toutes les pages du Gestionnaire de plug-in Megawizard et copiez tous les paramètres effectués par Megawizard sur ALTGX. Fermez Megawizard Manager.

4. La prochaine étape consiste à créer une nouvelle mégafunction ALTGX avec ATX PLL sélectionnée. Ouvrez à nouveau le Gestionnaire de plug-in Megawizard et cette fois créez une nouvelle mégafunction AltGX (située sous IO/ALTGX). Utilisez tous les paramètres copiés à l’étape 3. Cependant, cette fois, sélectionnez « Utiliser ATX PLL ».

5. Générer la nouvelle mégafunction ALTGX.

6. Localisez et ouvrez le fichier de conception qui instantanéise ALTGX dans l’IP Ethernet. Dans ce cas, le fichier est « altera_tse_gxb_gige_inst.v ». Remplacez l’ancien ALTGXB par le nouvel ALTGXB par un PLL ATX généré à l’étape 5.

Remarque : les nouveaux ports ALTGX ne possèdent pas de ports « fixedclk » et « fixedclk_fast ». Veillez à les commenter.

Le code ATXPLL ressemble à celui-ci après une modification :

générer si (DEVICE_FAMILY == || « STRATIXIV » DEVICE_FAMILY == « HARDCOPYIV »)

Commencer

altera_tse_alt4gxb_gige the_altera_tse_alt4gxb_gige // ALTGXB sans ATX PLL

my_ALTGX_with_ATXPLL the_altera_tse_alt4gxb_gige // ALTGXB avec ATX PLL

(

.cal_blk_clk (cal_blk_clk),

.fixedclk (wire_reconfig_clk),

.fixedclk_fast(1'b0),

.gxb_powerdown (gxb_powerdown),

7. Recompile la conception. Confirmez les modifications apportées au rapport d’installateur.

Le chiffre ci-dessous montre l’emplacement du cœur AltGX, « altera_tse_alt4gxb_gige », au sein du mégacore my_ethernet TSE.