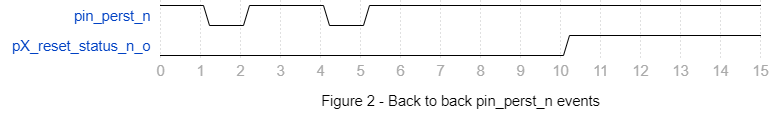

Le signal pX_reset_status_n_o du Intel® FPGA IP de streaming R-Tile Avalon® pour PCI Express inclut une caractéristique cumulée liée au nombre de d’pin_perst_n de 2 à 100 000.

Chaque événement de pin_perst_n dos sera mis en file d’attente et exécuté l’un après l’autre, affectant le temps total nécessaire au Intel® FPGA IP de streaming Avalon® R-Tile pour que PCI Express sorte de la réinitialisation et retire le signal pX_reset_status_n_o.

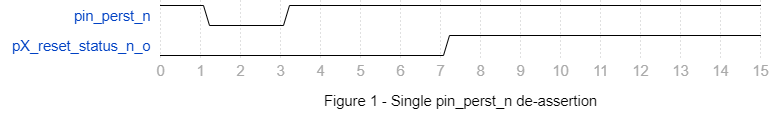

La Figure 1 montre la Intel® FPGA IP de streaming Avalon® R-Tile pour le comportement de PCI Express lorsqu’un seul pin_perst_n hôtes est délivré par l’hôte. La Figure 2 montre la caractéristique cumulée en cas d’émission de plusieurs pin_perst_n d’inhumateurs.

Le Intel® FPGA IP de streaming R-Tile Avalon® pour guide de l’utilisateur PCI Express a été mis à jour pour inclure ces informations à partir de la version 22.2.