En raison d’un problème dans le logiciel Intel® Quartus® Prime Pro Edition v21.4, une conception F-tile PMA/FEC Direct PHY Intel® FPGA IP contenant soit des émetteurs-récepteurs FGT ou FHT puissent afficher de manière incorrecte des pannes de synchronisation liées au contrôleur de réinitialisation soft (SRC).

Les caractéristiques de ces échecs de synchronisation sont que le lancement ou l’horloge du loquet seront répertoriés comme src_divided_osc_clk. L’autre horloge (l’horloge du loquet ou l’horloge de lancement) sera une horloge différente.

Vous pouvez également voir que le slack signalé est un nombre négatif très important, de l’ordre de -90 ns.

Voici des exemples de défaillances de synchronisation :

Exemple de défaillance de synchronisation 1

De nœud : IP_INST[0].hw_ip_top|dut|eth_f_0|sip_inst|sip_freeze_tx_src_reg[0]

Au nœud : eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl_sync|sip_freeze_tx_SRC_sequence_inst[18]|din_s1

Horloge de lancement : reconfig_clk

Horloge de loquet : src_divided_osc_clk

Modèle de retard : configuration 2_slow_vid2_100c : -1.474 hold : 0.027

Modèle de retard : configuration 2_slow_vid2b_100c : -1,574 hold : 0.167

Modèle de retard : configuration MIN_fast_vid2a_0c : -1.193 hold : 0.216

Modèle de retard : configuration MIN_fast_vid2a_100c : -1.304 hold : 0.186

Modèle de retard : configuration MIN_fast_vid2_100c : -1.244 hold : 0.093

Exemple de défaillance de synchronisation 2

De nœud : eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl|dp_sip_rx_aib_control_select[19]

Au nœud : eth_f_hw__tiles|z1577a_x0_y0_n0|hdpldadapt_rx_chnl_19~pld_rx_clk1_dcm.reg

Horloge de lancement : src_divided_osc_clk

Horloge de loquet : IP_INST[0].hw_ip_top|clkdiv2_pll_inst|altera_iopll_0_outclk0

Modèle de retard : récupération 2_slow_vid2_100c : -90.597 suppression : 0.244

Modèle de retard : récupération 2_slow_vid2b_100c : -90.756 suppression : 0.446

Modèle de retard : récupération MIN_fast_vid2a_0c : suppression -90.063 : 0.535

Modèle de retard : récupération MIN_fast_vid2a_100c : -90.241 suppression : 0.316

Modèle de retard : récupération MIN_fast_vid2_100c : suppression -90.057 : 0.076

Ce problème est résolu à partir du logiciel Intel® Quartus® Prime Pro Edition v22.1.

Pour contourner ce problème dans la version 21.4 ou antérieure du logiciel Intel® Quartus® Prime Pro Edition, les chemins défectueux liés au contrôleur de réinitialisation logicielle peuvent être ignorés en toute sécurité.

Cependant, si vous choisissez de corriger ces défaillances de synchronisation incorrectes afin qu’elles ne soient pas signalées, suivez ces étapes :

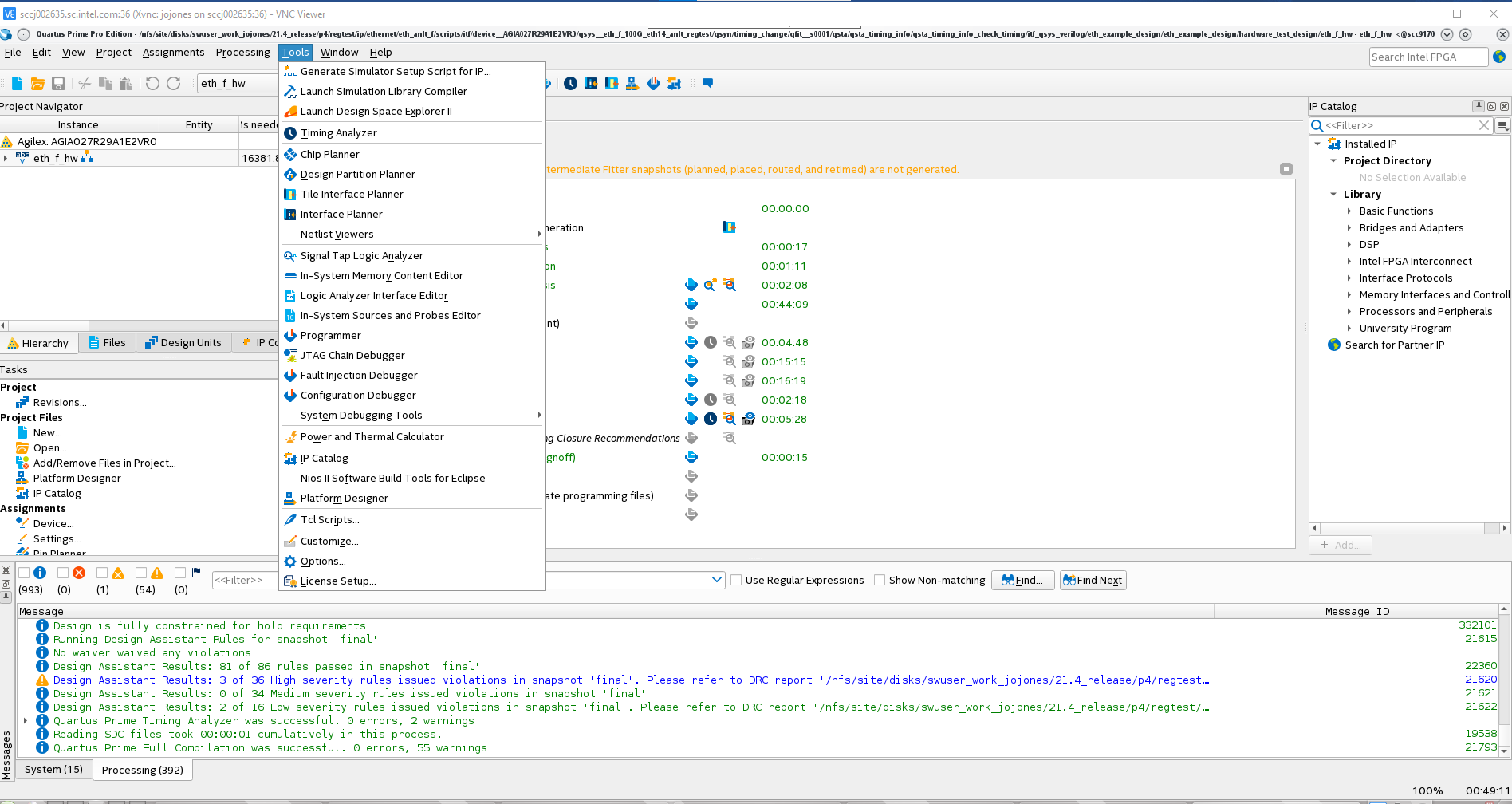

- ) Une fois que vous avez compilé votre conception dans le logiciel Intel® Quartus® Prime, lancez l’Analyseur de synchronisation à partir du menu Outils .

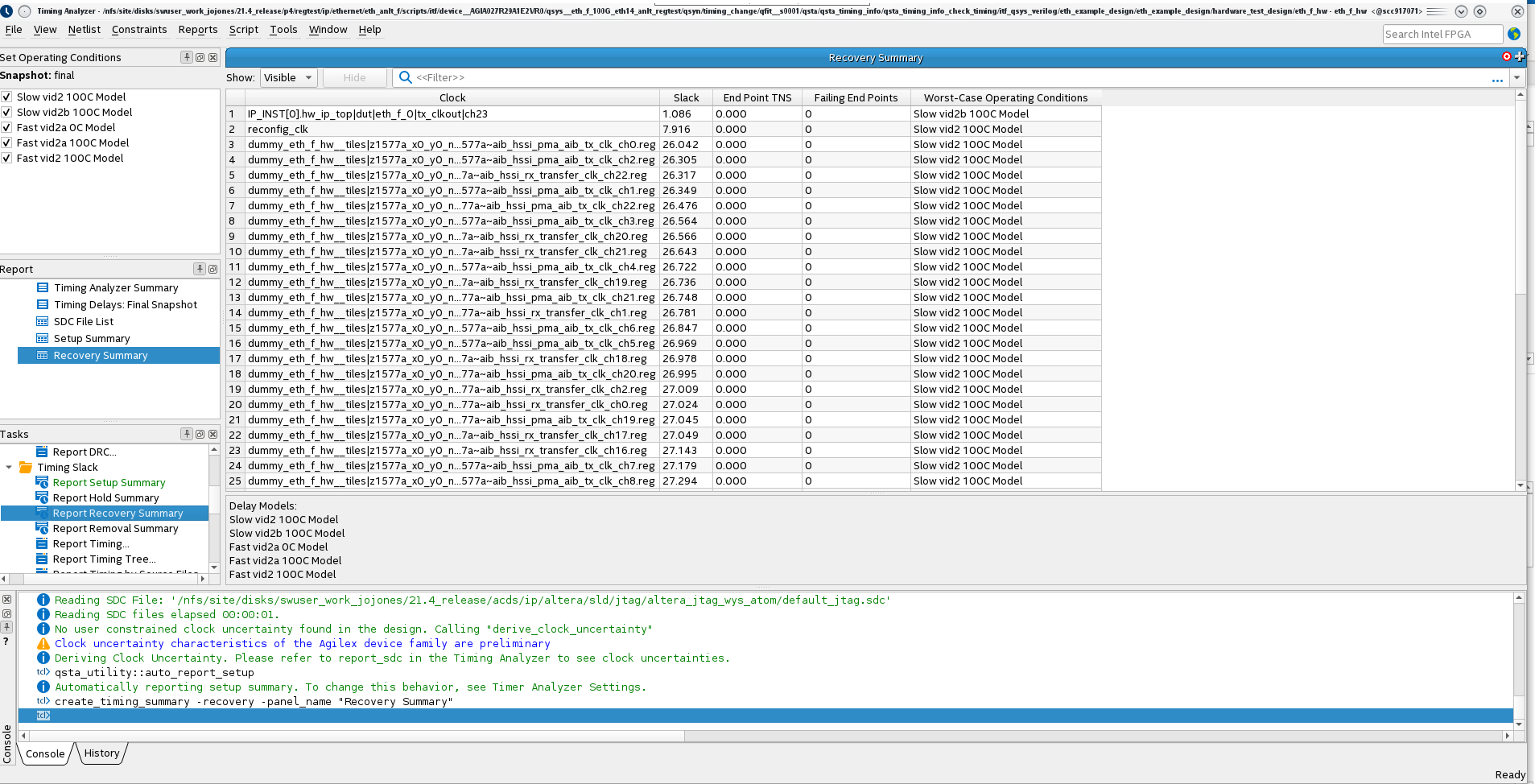

- ) Après que l’Analyseur de synchronisation a créé la netlist de synchronisation, Générer divers rapports de synchronisation, notamment le rapport de synchronisation de la configuration et le rapport de synchronisation de récupération.

Dans ce cas, même si les faux chemins ne sont pas limités, l’analyseur de synchronisation ne signale aucune erreur de synchronisation.

-

) Regardez le rapport du croisement de domaines d’horloge pour voir les chemins de synchronisation non entraînés.

Cela montre les chemins de synchronisation non entraînés comme Asynchrone (timed unsafe). Même si l’Analyseur de synchronisation ne signale pas d’erreur de synchronisation pour ces chemins, il doit être limité afin qu’ils ne soient pas inclus dans l’analyse de synchronisation.

Cela montre les chemins de synchronisation non entraînés comme Asynchrone (timed unsafe). Même si l’Analyseur de synchronisation ne signale pas d’erreur de synchronisation pour ces chemins, il doit être limité afin qu’ils ne soient pas inclus dans l’analyse de synchronisation. -

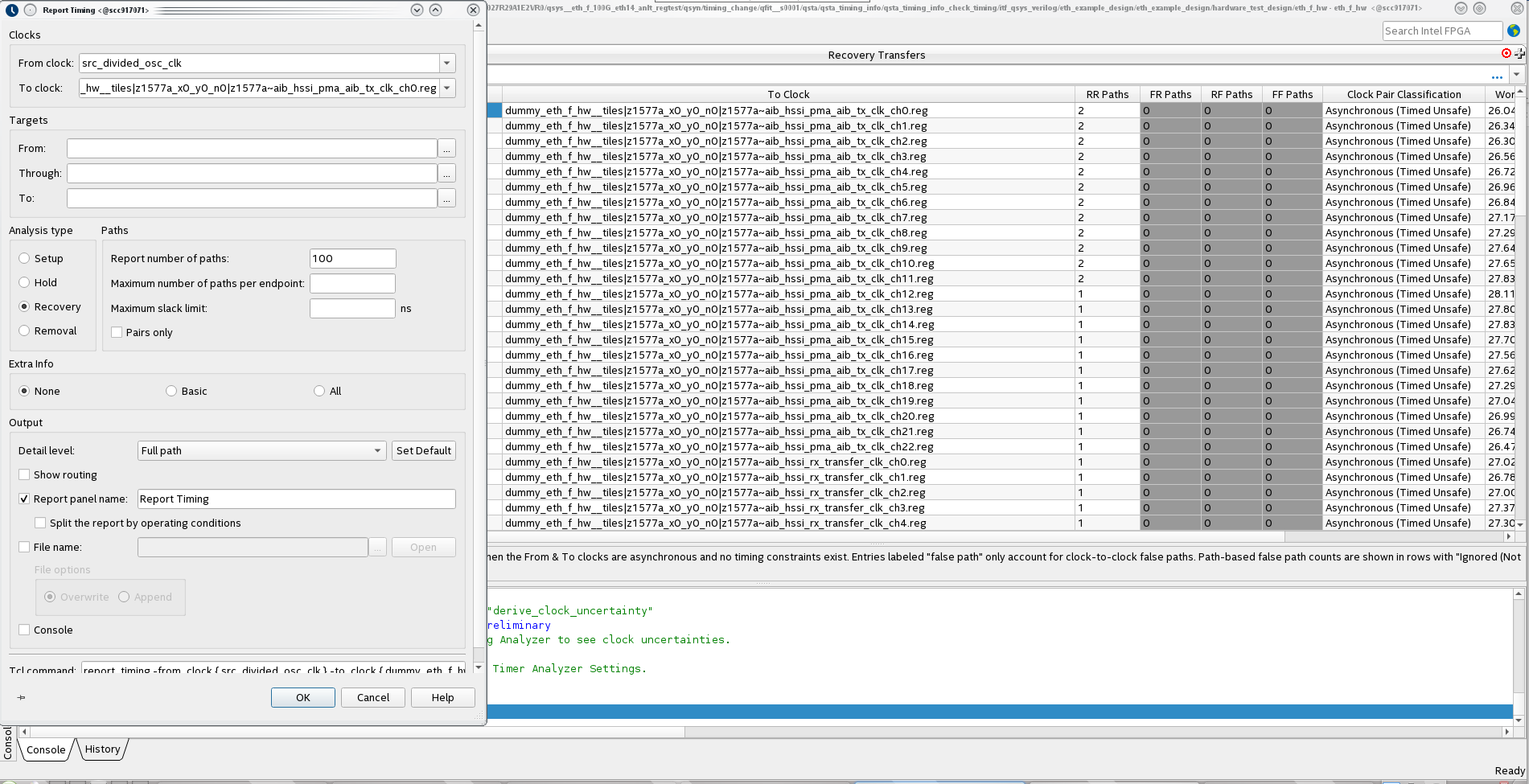

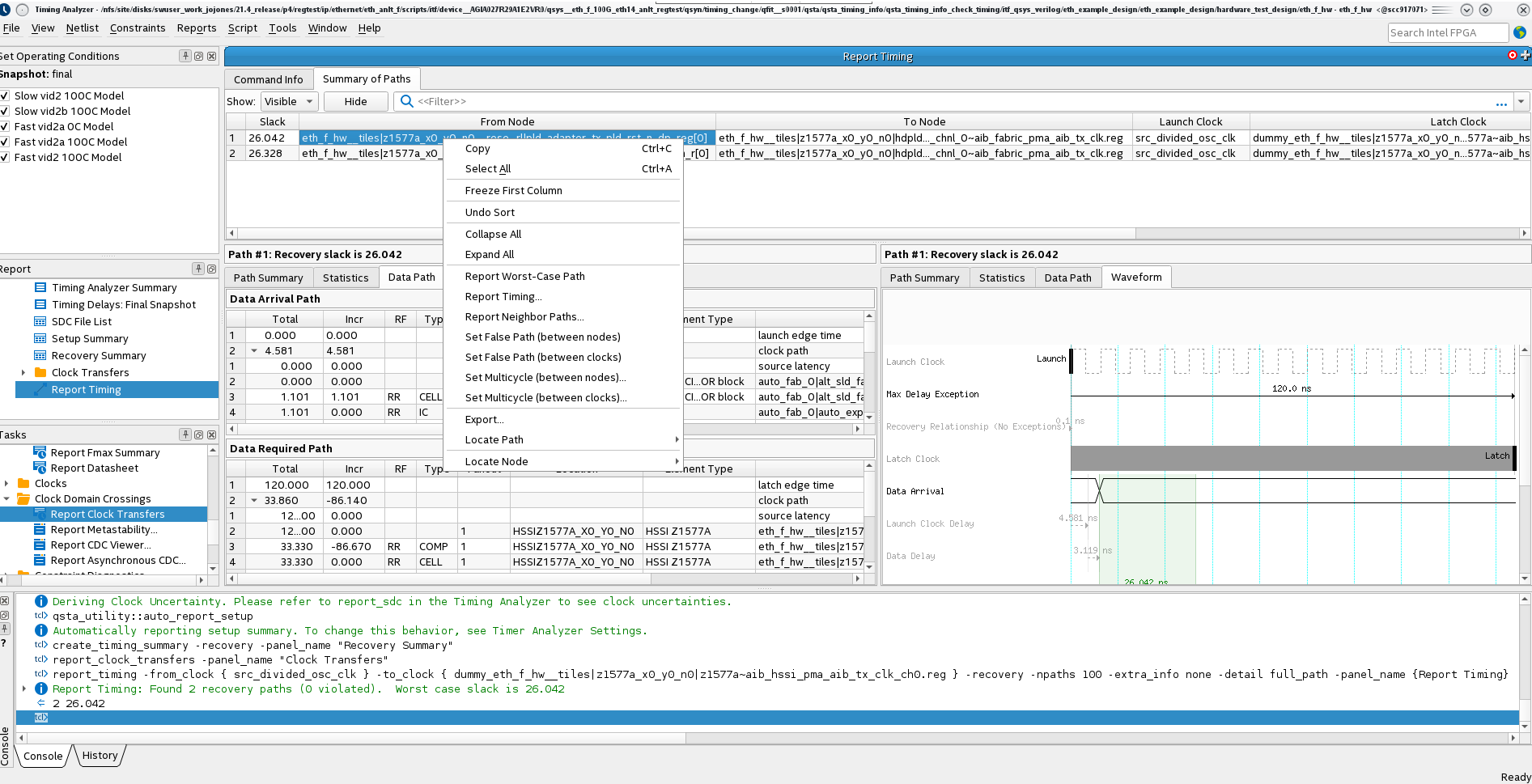

) Pour définir une contrainte sur ces chemins, sélectionnez l’un d’entre eux, cliquez avec le bouton droit sur la souris et sélectionnez Report Timing. Les options par défaut du rapport telles qu’elles sont indiquées sont suffisantes.

-

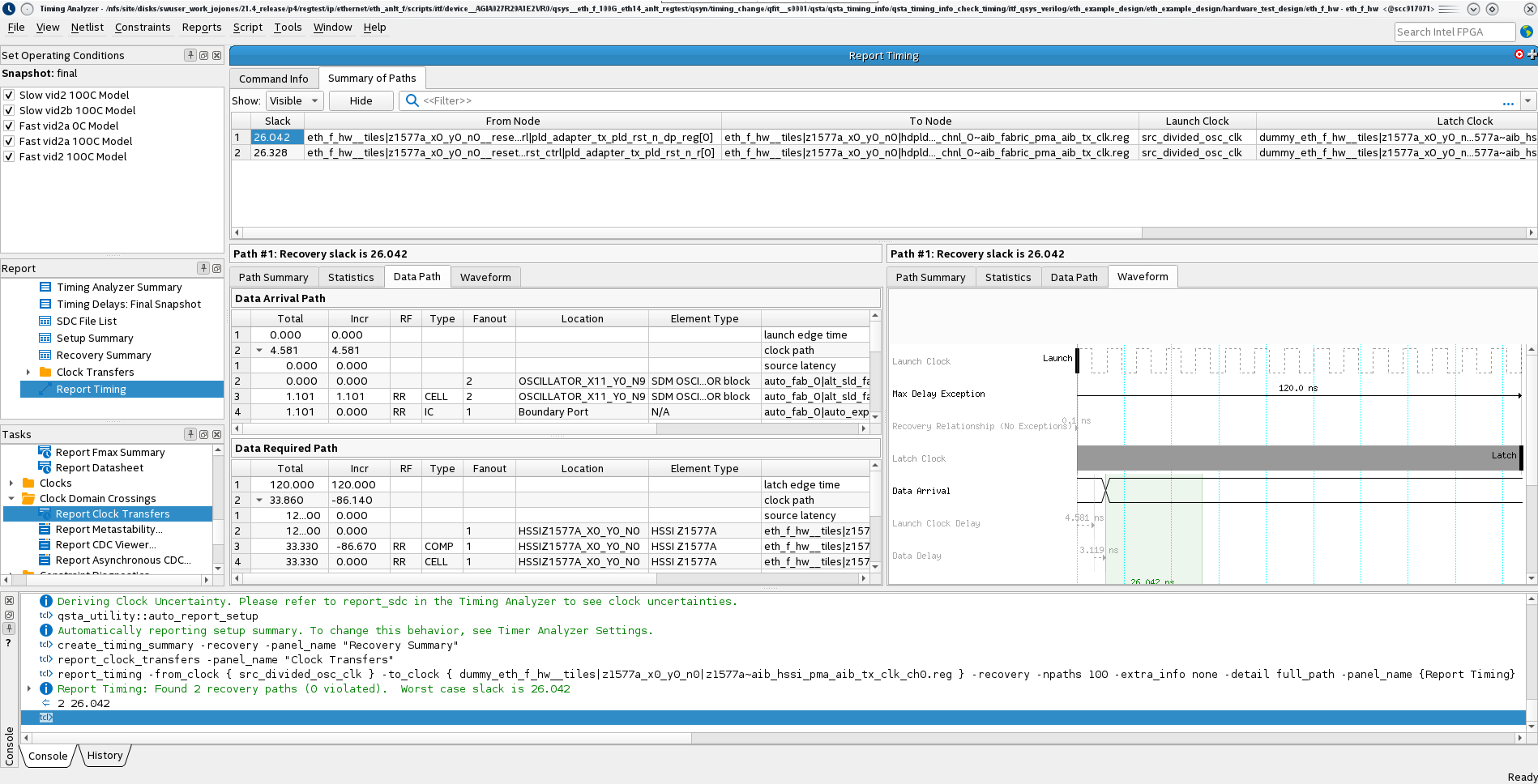

) Cliquez sur OK. Le rapport de synchronisation sera produit.

-

) Pour limiter le chemin en tant que Faux Chemin, ce qui signifie qu’il ne sera plus inclus dans l’analyse de synchronisation, cliquez avec le bouton droit n’importe où sur le chemin et sélectionnez Définir de faux chemin (entre les nœuds)...

-

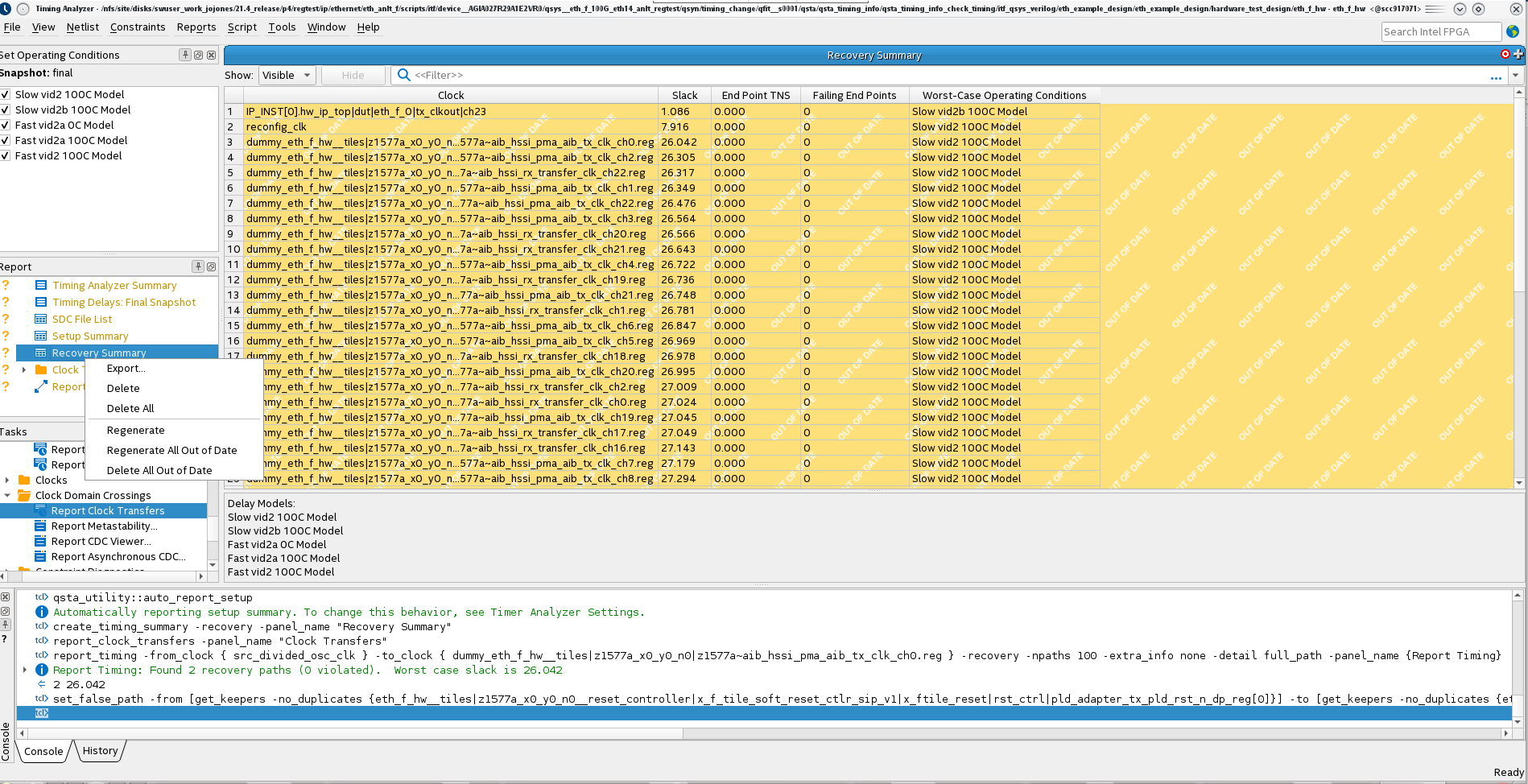

) Pour supprimer les rapports de synchronisation, cliquez avec le bouton droit sur l’un des rapports indiqués dans la fenêtre Du rapport et sélectionnez Une résipateur de demande tous obsolète.

Après avoir présenté des rapports obsolètes, vous verrez que la voie de synchronisation que vous avez limitée n’apparaît plus dans le rapport sommaire. Cela s’explique par le fait que vous avez contraint l’analyseur de synchronisation à ne pas analyser cette fausse voie.

Après avoir présenté des rapports obsolètes, vous verrez que la voie de synchronisation que vous avez limitée n’apparaît plus dans le rapport sommaire. Cela s’explique par le fait que vous avez contraint l’analyseur de synchronisation à ne pas analyser cette fausse voie. -

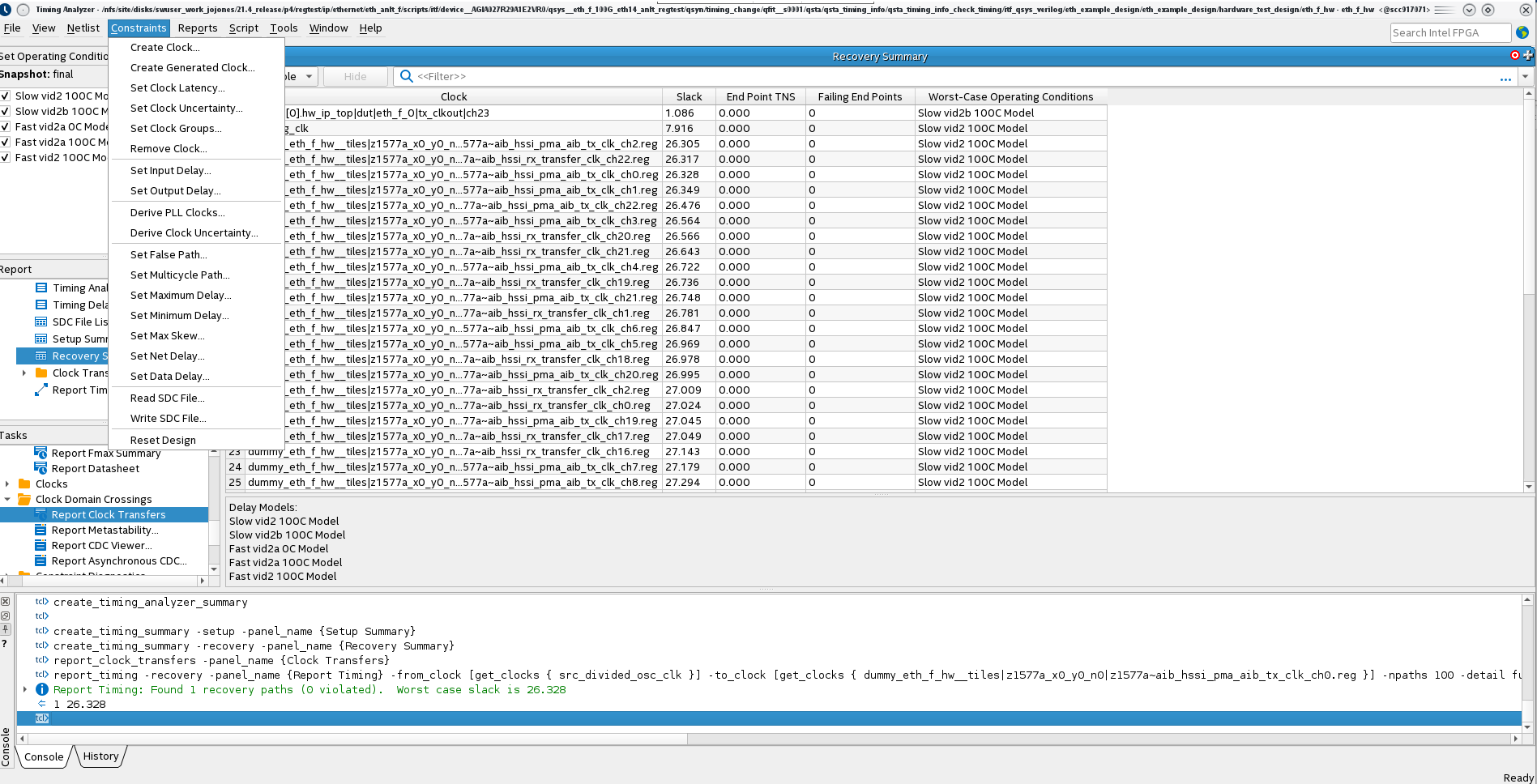

) Répétez cela pour tous les chemins que vous souhaitez limiter. Une fois que vous avez terminé, enregistrez toutes les modifications que vous avez apportées dans un nouveau fichier .sdc en sélectionnant Write SDC File... dans le menu Contraintes .

Vous pouvez sélectionner le nom et l’emplacement du fichier .sdc à écrire.

Le fichier .sdc généré inclut toutes les contraintes des fichiers .sdc initialement lus pour la conception, ainsi que la nouvelle contrainte que vous avez ajoutée.

Vous pouvez ajouter ce fichier .sdc à votre projet logiciel Intel Quartus Prime pour les compilations futures.

Ce problème devrait être résolu dans une prochaine version du logiciel Intel Quartus Prime Pro Edition.