Cette erreur peut être constatée dans Intel® Quartus® logiciel Prime Pro Edition lors de la compilation de toutes les Intel Agilex® conception ciblée de périphérique qui contient la conception d’interface générique Serial Flash Intel® FPGA IP avec les conduits exportés. Cela s’explique par un conflit d’activation de sortie (OE) dans le placement des broches de conception. L’erreur peut être dupliquée sur différentes affectations de broches si plusieurs conflits d’oes sont détectés.

Dans tous les périphériques Intel Agilex, il existe une exigence de placement des broches en raison du fait que le matériel OEM est partagé entre x4 broches du groupe DQ. Ainsi, s’il existe deux canaux possédant leurs propres signaux OEM respectifs, ils doivent être affectés à différents broches du groupe DQ x4 pour éviter les conflits d’oem.

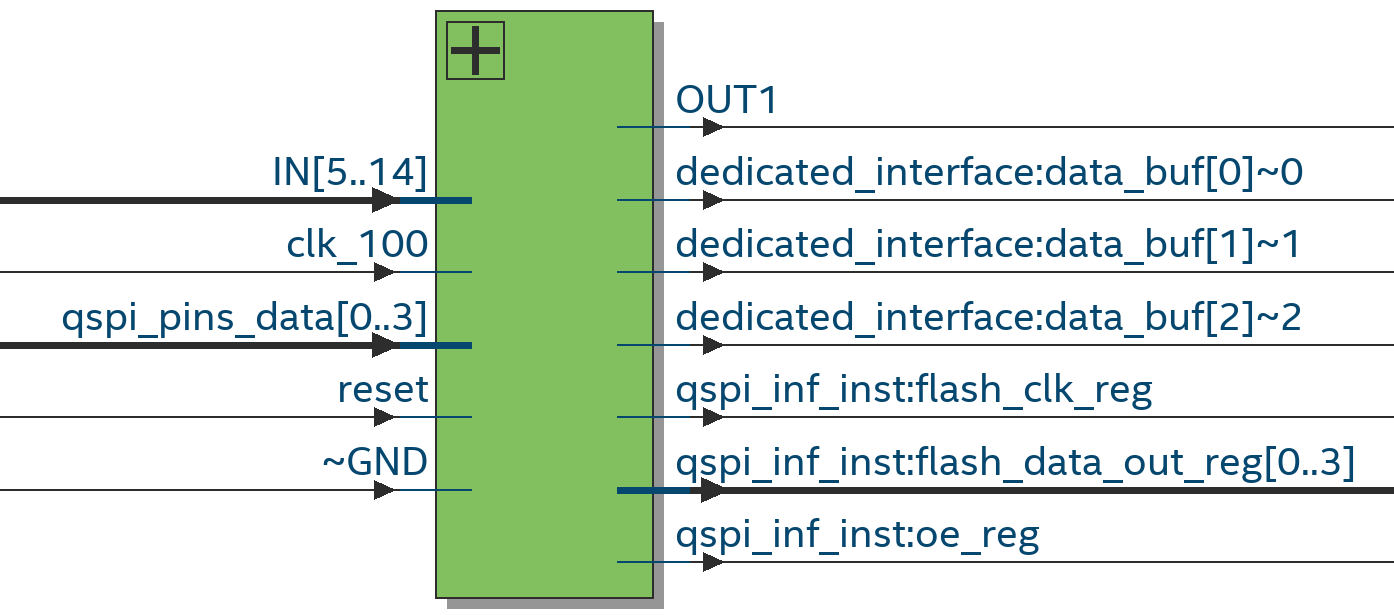

Intel FPGA IP d’interface Serial Flash générique (consultée dans Technology Map Viewer)

| Signaux OE | Conduits exportés |

|---|---|

| dedicated_interface:data_buf[0]~0 | qspi_pins_data[0] |

| dedicated_interface :data_buf[1]~1 | qspi_pins_data[1] |

| dedicated_interface :data_buf[2]~2 | qspi_pins_data[2] qspi_pins_data[3] |

| qspi_inf_inst :oe_reg | qspi_pins_dclk qspi_pins_ncs |

Pour éviter cette erreur, les conduits exportés avec différents signaux OE doivent être créés dans un groupe DQ x4 différent, tandis que les conduits exportés avec un signal OE partagé sont recommandés pour être établis au sein du même groupe x4 DQ. Le tableau suivant présente un exemple utilisant un périphérique Intel Agilex® (AGFB027) :

| Conduits exportés | Placement des broches | x4 groupes DQ (AGFB027) |

|---|---|---|

| qspi_pins_data[0] | W34 | DQ133 |

| qspi_pins_data[1] | J35 | DQ135 |

| qspi_pins_data[2] qspi_pins_data[3] | L38 W38 | DQ132 |

| qspi_pins_dclk qspi_pins_ncs | J39 C38 | DQ134 |

Les informations sont disponibles dans Intel® Agilex™ Guide de l’utilisateur des E/S et LVDS SERDES à usage général et les fichiers pin-out pour Intel FPGA.